Alpinum Consulting CEO Mike Bartley has contributed an article to EE Times on one of the most active questions in semiconductor verification today: where AI can help design verification teams, and where engineering confidence still depends on human judgment.

The article, “AI in Design Verification: Where It Works and Where It Doesn’t,” is now live on EE Times.

Why this article matters

AI is now part of the verification conversation, but adoption needs discipline. The issue is not whether AI can assist engineers. It can. The real question is where it can be introduced without weakening traceability, coverage discipline, or sign-off confidence.

In the EE Times article, Mike explains that AI is most useful in bounded, data-rich verification workflows such as regression analysis, coverage closure support, and bug triage. These are areas where repetitive analysis, prioritisation, and pattern recognition can reduce engineering overhead.

However, the article also makes a clear distinction: verification is not only a productivity problem. It is a confidence problem. Sign-off still depends on evidence, review, engineering judgement, and an understanding of residual risk.

Key themes covered in the EE Times article

The article discusses several practical points for engineering teams:

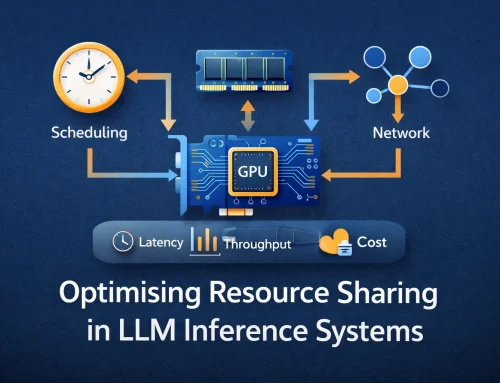

- AI can support repetitive verification tasks where outputs can be reviewed and validated.

- Regression noise remains a major source of wasted engineering effort, especially when teams need to separate genuine new failures from duplicate or low-value results.

- System-level verification remains difficult because many critical bugs emerge from subsystem interactions, timing dependencies, protocol behaviour, or long-running states.

- AI adoption must fit existing verification workflows rather than bypass them.

These points are particularly relevant for teams working on complex SoCs, multi-domain architectures, and verification environments where confidence and traceability are central to delivery.

A practical message for verification teams

The most useful framing is not “Can AI do verification?” A better question is:

Which parts of the verification workload are repetitive, observable, and measurable enough for AI assistance without weakening engineering confidence?

That question keeps AI adoption grounded in real verification practice rather than abstract automation claims.

Read the full article

For the full technical perspective, read Mike Bartley’s article on EE Times:

Work with Alpinum Consulting

If your organisation is exploring AI in design verification, the challenge is not selecting tools—it is integrating them into real engineering workflows.

At Alpinum Consulting, we work with semiconductor teams to:

- Improve verification efficiency

- Reduce regression overhead

- Strengthen sign-off confidence

- Align AI adoption with engineering reality

Stay Connected

Follow Mike Bartley for insights on:

- AI in design verification

- System-level challenges

- RISC-V and advanced verification flows

Written by : Mike Bartley

Mike started in software testing in 1988 after completing a PhD in Math, moving to semiconductor Design Verification (DV) in 1994, verifying designs (on Silicon and FPGA) going into commercial and safety-related sectors such as mobile phones, automotive, comms, cloud/data servers, and Artificial Intelligence. Mike built and managed state-of-the-art DV teams inside several companies, specialising in CPU verification.

Mike founded and grew a DV services company to 450+ engineers globally, successfully delivering services and solutions to over 50+ clients.

Mike started Alpinum in April 2025 to deliver a range of start-of-the art industry solutions:

Alpinum AI provides tools and automations using Artificial Intelligence to help companies reduce development costs (by up to 90%!) Alpinum Services provides RTL to GDS VLSI services from nearshore and offshore centres in Vietnam, India, Egypt, Eastern Europe, Mexico and Costa Rica. Alpinum Consulting also provides strategic board level consultancy services, helping companies to grow. Alpinum training department provides self-paced, fully online training in System Verilog, UVM Introduction and Advanced, Formal Verification, DV methodologies for SV, UVM, VHDL and OSVVM and CPU/RISC-V. Alpinum Events organises a number of free-to-attend industry events

You can contact Mike (mike@alpinumconsulting.com or +44 7796 307958) or book a meeting with Mike using Calendly (https://calendly.com/mike-alpinum-consulting).

Stay Informed and Stay Ahead

Latest Articles, Guides and News

Explore related insights from Alpinum that dive deeper into design verification challenges, practical solutions, and expert perspectives from across the global engineering landscape.