Electronic systems are becoming harder to verify with simulation alone. As processor architectures grow more configurable, interconnected, and software-dependent, verification teams are increasingly dealing with state-space complexity that traditional regression approaches cannot fully explore.

Mike Bartley, CEO of Alpinum Consulting, discusses this challenge in the latest edition of Electronics World through his published column:

“The Growing Role of Formal Verification in RISC-V Design”

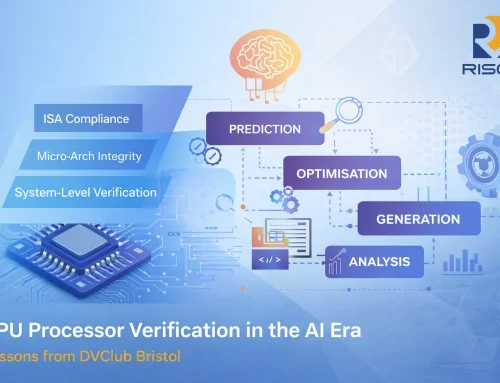

The article examines why formal methods are becoming increasingly important in modern RISC-V verification flows, particularly as ISA flexibility, privilege modes, CSR behaviour, and cross-domain interactions increase architectural complexity.

Read the Full Published Column here:

👉 Free Access Electronics World Column

Why this topic matters

Simulation remains essential in semiconductor verification, but it cannot exhaustively explore all reachable states in increasingly configurable processor architectures.

The article explains why formal verification is no longer viewed only as an advanced specialist technique. Instead, it is becoming a practical verification layer used to strengthen correctness assurance, particularly in:

- RISC-V processor verification

- ISA compliance validation

- CSR and privilege handling

- Safety-critical design verification

- Protocol and control logic verification

- Hybrid verification flows combining simulation and formal analysis

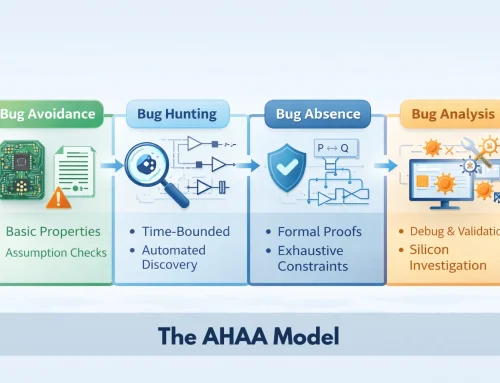

A central theme in the article is that formal verification changes the nature of the verification claim. Rather than increasing sampled behavioural coverage, formal analysis attempts to prove mathematically that the defined properties hold across all reachable states in a constrained model.

Key themes covered in the column

Simulation coverage does not equal proof

Simulation can increase behavioural exploration, but unexplored regions of state space still remain. The article discusses how formal techniques address this limitation by evaluating properties across reachable state combinations rather than sampled scenarios.

RISC-V increases verification complexity

The modular and extensible nature of the RISC-V ISA creates new verification challenges across:

- Optional ISA extensions

- Privilege architectures

- CSR behaviour

- Security isolation

- Interrupt handling

- Configurable implementations

These architectural freedoms significantly expand the verification surface.

Formal verification is becoming operationally practical

The article explains why formal verification is increasingly being integrated into production verification flows rather than remaining an isolated research activity.

This includes:

- Property checking

- Control logic verification

- Security verification

- Hybrid formal/simulation methodologies

- Structured sign-off support

Discipline matters more than tooling alone

One of the strongest points in the column is that successful formal adoption depends heavily on engineering discipline.

That includes:

- Correct property specification

- Constraint definition

- Decomposition strategy

- Verification planning

- Methodology integration

Formal methods require operational rigour, not simply additional tooling.

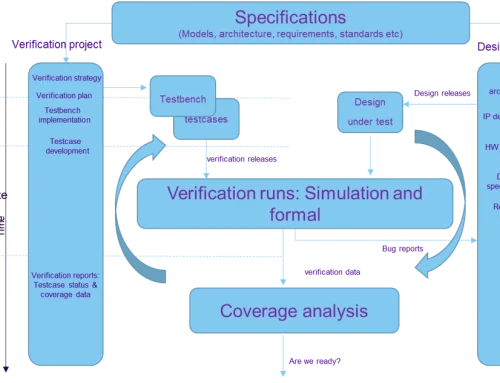

Hybrid verification is becoming the practical direction

The column also explores how many teams now combine simulation and formal verification rather than treating them as competing methodologies.

Simulation remains valuable for:

- Broad behavioural exploration

- Software interaction analysis

- System-level visibility

Formal verification strengthens:

- Proof-based correctness

- Corner-case exploration

- Control-path analysis

- Assertion-driven verification

Together, these approaches improve engineering confidence in increasingly complex RISC-V systems.

Engineering implication for verification teams

As architectures become more configurable and verification schedules tighten, verification teams are increasingly forced to reconsider how confidence is established.

The question is no longer whether simulation is useful.

The question is whether simulation alone remains sufficient for proving correctness in increasingly complex systems.

That distinction is becoming especially important in:

- Automotive systems

- Industrial control

- Secure embedded platforms

- Safety-critical semiconductor environments

Read the full article

For the full technical perspective, read Mike Bartley’s article in Electronics World Issue:

👉 The Growing Role of Formal Verification in RISC-V Design

Continue the discussion

For teams evaluating structured verification strategies, formal methodologies, or scalable RISC-V verification approaches:

- Learn more about Alpinum Consulting’s verification expertise: Design Verification Services

- Explore Alpinum training programmes: Verification Training Services

- Book a discussion with Mike Bartley: Schedule a Meeting

Written by : Mike Bartley

Mike started in software testing in 1988 after completing a PhD in Math, moving to semiconductor Design Verification (DV) in 1994, verifying designs (on Silicon and FPGA) going into commercial and safety-related sectors such as mobile phones, automotive, comms, cloud/data servers, and Artificial Intelligence. Mike built and managed state-of-the-art DV teams inside several companies, specialising in CPU verification.

Mike founded and grew a DV services company to 450+ engineers globally, successfully delivering services and solutions to over 50+ clients.

Mike started Alpinum in April 2025 to deliver a range of start-of-the art industry solutions:

Alpinum AI provides tools and automations using Artificial Intelligence to help companies reduce development costs (by up to 90%!) Alpinum Services provides RTL to GDS VLSI services from nearshore and offshore centres in Vietnam, India, Egypt, Eastern Europe, Mexico and Costa Rica. Alpinum Consulting also provides strategic board level consultancy services, helping companies to grow. Alpinum training department provides self-paced, fully online training in System Verilog, UVM Introduction and Advanced, Formal Verification, DV methodologies for SV, UVM, VHDL and OSVVM and CPU/RISC-V. Alpinum Events organises a number of free-to-attend industry events

You can contact Mike (mike@alpinumconsulting.com or +44 7796 307958) or book a meeting with Mike using Calendly (https://calendly.com/mike-alpinum-consulting).

Stay Informed and Stay Ahead

Latest Articles, Guides and News

Explore related insights from Alpinum that dive deeper into design verification challenges, practical solutions, and expert perspectives from across the global engineering landscape.