Formal Verification Services for ASIC and SoC Development

Alpinum provides advanced formal verification services that help semiconductor teams mathematically prove design correctness, uncover complex corner-case bugs, and strengthen verification confidence in modern ASIC and SoC architectures.

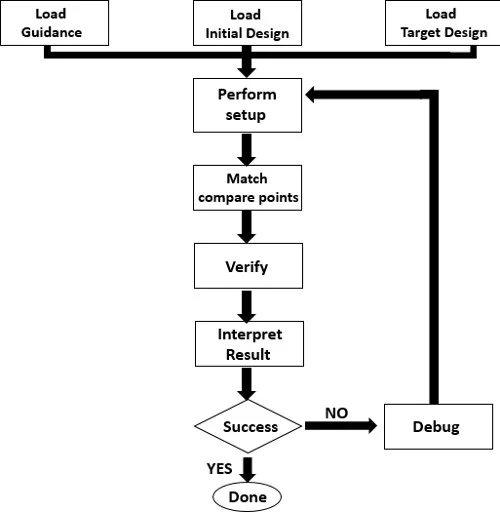

As semiconductor systems become increasingly complex, simulation alone cannot guarantee full verification coverage. Formal verification techniques such as property checking, model checking, and equivalence verification allow engineers to analyse design behaviour exhaustively and detect subtle design errors early in development.

Alpinum Consulting supports design teams in integrating formal verification into real verification workflows, improving design quality while reducing silicon risk.

The Growing Verification Challenge

in Modern Semiconductor Design

Semiconductor designs today integrate multiple subsystems including processors, accelerators, security modules, and high-speed communication interfaces. As system complexity grows, verification effort often accounts for the majority of engineering work within ASIC programmes.

Simulation-based verification remains essential, particularly when using structured methodologies such as Universal Verification Methodology environments. However, simulation cannot exhaustively explore all possible system behaviours. Rare corner cases involving protocol interactions, arbitration logic, or state transitions may remain undetected until late in the design cycle.

Formal verification addresses these limitations by applying mathematical analysis to the design model, allowing engineers to prove that specific behavioural properties always hold true.

Capabilities of Formal Verification

Formal verification provides engineers with a fundamentally different approach to validating hardware behaviour. Instead of generating stimulus and observing results, formal tools explore the reachable state space of a design and determine whether defined properties can ever be violated.

This allows engineers to detect issues such as:

Formal techniques are particularly effective for verifying control logic and protocol behaviour in complex SoCs.

Key Techniques Used in Formal Verification

Tools Used in Formal Verification Projects

Formal verification environments typically integrate several semiconductor verification technologies. Engineers define behavioural properties using constructs available in SystemVerilog assertion languages. Formal analysis is performed using industry tools developed by companies such as:

These tools provide capabilities including model checking, property verification, and equivalence analysis. Formal environments are frequently integrated with simulation environments built using Universal Verification Methodology.

Where Formal Verification Is Used

Formal Verification Consulting from Alpinum

Alpinum Consulting supports semiconductor design teams by integrating formal verification techniques into practical verification workflows. Our consultants help organisations identify design components that benefit from formal analysis and develop property specifications aligned with design requirements.

We also support verification teams in interpreting formal verification results and integrating formal analysis with simulation-based verification flows. This approach allows semiconductor organisations to improve verification coverage, detect subtle design errors earlier, and reduce the risk of silicon respins.

Ready to strengthen your formal verification strategy?

Whether you are validating complex control logic, introducing formal verification techniques into your verification flow, or improving property coverage before tape-out, Alpinum can support your team with experienced formal verification specialists and practical engineering delivery.

Formal Verification Services and

Specialised Verification Solutions

Design teams exploring formal verification also work with broader Design Verification Services, including Pre-Silicon Verification and Post-Silicon Validation.

These connections reinforce Alpinum’s expertise across the semiconductor verification lifecycle.

Discuss Your Formal Verification Challenges

Alpinum Consulting helps semiconductor organisations implement practical verification strategies that improve design confidence and reduce silicon risk.

Prefer direct email?

Write to mike@alpinumconsulting.com

Book a quick meeting with Mike:

https://calendly.com/mike-alpinumconsulting