ASIC Design Verification Services and SoC Verification Consulting

Engineering-Led Semiconductor Design Verification Services

Modern semiconductor systems integrate billions of transistors, complex IP blocks, and highly configurable architectures. As chip complexity increases, verification has become the most demanding stage of silicon development.

Many organisations now rely on specialised ASIC verification services and SoC verification consulting to ensure their designs behave correctly before fabrication.

Alpinum Consulting works with semiconductor companies worldwide to strengthen verification strategies, improve coverage, and resolve verification bottlenecks in demanding silicon projects.

Our engineers provide semiconductor design verification services across ASIC, FPGA, and embedded system development, helping organisations deliver reliable silicon with confidence.

Industry Challenges in Semiconductor Design Verification

Verification effort in modern semiconductor projects typically represents 60–80% of the overall engineering workload. As architectures evolve, the difficulty of ensuring correct behaviour across all operating conditions continues to increase.

Alpinum Expertise in ASIC and SoC Verification

Alpinum Consulting provides ASIC design verification services and SoC verification consulting to semiconductor companies developing advanced silicon systems.

ASIC Design Verification Services for Modern SoC Development

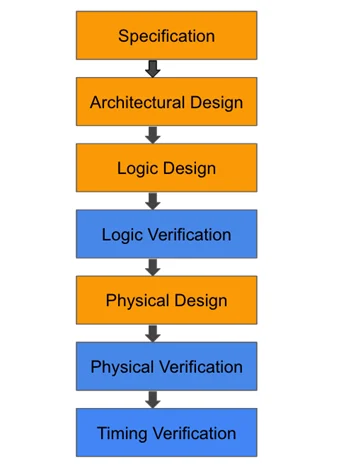

Design Verification Methodology

Effective verification requires structured engineering processes that ensure all design behaviours are systematically validated.

ASIC Verification Services and Consulting Capabilities

Alpinum provides semiconductor design verification services covering the entire verification lifecycle.

Tools and Technologies

Typical technologies used in semiconductor verification projects include:

Industries Served

Design verification consulting supports semiconductor development across many industry sectors.

Why Semiconductor Companies Choose Alpinum

Several factors distinguish Alpinum Consulting within the semiconductor consulting ecosystem.

Consulting Engagement Models

Semiconductor companies can work with Alpinum through several engagement approaches.

Ready to de-risk your ASIC or SoC verification programme?

Whether you are verifying a new ASIC architecture, integrating third-party IP, or strengthening verification coverage before tape-out, Alpinum can support your team with experienced silicon verification experts and practical engineering delivery.

Design Verification Services and

Specialised Verification Solutions

Discuss Your Design Verification Project with Our Engineers

Our team supports semiconductor companies developing complex ASIC and SoC architectures across Europe, the UK, and global markets.

Prefer direct email?

Write to mike@alpinumconsulting.com

Book a quick meeting with Mike:

https://calendly.com/mike-alpinumconsulting